CPU features

AMD's server solutions are flexible, with Turbo Core, Core select to select via BIOS the number of visible cores (for example to reduce software license costs), various modes of operation of FLEX FP, cache partitioning and new HPC instructions (FMA4 and XOP, AMD's unique, and AVX, and cryptographic acceleration, shared with INTEL), TDP power cap, to limit the power dissipated by the CPU with 1W granularity, C6 state, for a lower IDLE consumption, 6 TDP classes to choose the CPU that best suits your needs, support for low and ultra low voltage DIMMs, support from 4 to 64 cores per rack with the same chipset (and drivers) for all systems from 1 to 4 sockets.

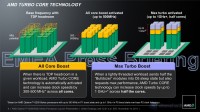

The Turbo core technology is active both with all cores active, in which case allows for an increase from 300 to 500MHz depending on the model and with a maximum of half of the core active of up to 1.2GHz (for the top 16 core model).

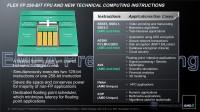

As we saw in the Bulldozer architecture presentation, each module has a shared FPU, capable of executing 128 and 256 bits instructions of two threads.

The supported FPU instruction set are:

- x87, MMX, SSE1, SSE2, SSE3, which is the FPU and Integer legacy instruction set, both scalar SIMD, supported by both AMD and Intel;

- SSSE3, SSE4.1, SSE4.2, which is the FPU and integer SIMD set, supported by both AMD and Intel, which speeds up the video algorithms, biometric and intensive text processing;

- AESNI, PCLMULQDQ, which is the instruction set, common to both AMD and Intel, that accelerate cryptographic algorithms, and in particular the AES;

- AVX, which is the new instruction set, shared by both AMD and Intel, with a new extensible encoding, allowing you to have FPU and integer SIMD instructions both 128 and 256 bits, and that serves to accelerate compute-intensive applications, such as HPC;

- FMA4, AMD's unique instruction set, which allows 4-way operations of multiplication and accumulation in a single instruction, greatly speeding up the algorithms that require them, such as matrix multiplication, and many scientific calculations;

- XOP, AMD's unique instruction set, which contains instructions for accelerating multimedia applications, as the sum of vectors, fraction extraction and conversion for 16-bit FP numbers, used in video cards.

These sets of instructions were designed to increase the instructions calculation density, to reduce the need to copy registers (only FMA4) and to allow automatic vectorization by compilers.